Intel CEO Pat Gelsinger: Intel nimmt TSMC-Wafer an und will zu Tick-Tock zurück

Intels CEO Pat Gelsinger hat mehr Informationen zum neuen Foundry-Modell und zum zuletzt ad acta gelegten Tick-Tock-Modell preisgegeben. Kunden von Intels neuer Foundry sollen demnach sogar ihre TSMC-Wafer mitbringen und bei Intel im Packaging fertigstellen lassen können, das altbekannte Tick-Tock-Modell sei zurück in der Spur.

Foundry 2.0: Bring your own belichtete Wafer

Einmal mehr präsentiert Intels neuer CEO die Foundry 2.0 als Allheilmittel, was in Zeiten wie diesen aber auch leicht funktioniert: Kapazitäten in Fabriken sind überall knapp, wenn nicht gar auf viele Monate ausgebucht, weshalb es auch nicht überrascht, dass Intel bereits „über 100 Kunden“ für das neue Foundry-Modell vermeldet.

Um damit nicht nur Intels neue EUV-Belichtungsmaschinen mit neuen Kunden auszulasten, wirbt Intel auch mit seinem fortschrittlichen Package: Kunden könnten in Zukunft auch ihre bei TSMC fertig belichteten Wafer mitbringen und sie in Intels Werken auf ihr Package setzen lassen. Technologien wie EMIB und Foveros sind bisher exklusiv bei Intel zu haben, der Hersteller forscht zudem weiterhin massiv auf dem Gebiet der Packaging-Technologien.

I've customers today that are saying, can I take my TSMC wafer and run it through your world leading packaged assembly and test? And the answer is yes. We're also making all of our x86 and other core IP available, Intel graphics, Intel networking, Intel big core, Intel little core, things that were never made available before to foundry customers. Those are being made available for our foundries and we're seeing particular interest for what I'll call these hybrid designs from the large scale cloud guys.

Intel-CEO Pat Gelsinger

Tick-Tock-Modell und jährlich neue Chips

Nicht weniger groß sind die Versprechen hinsichtlich des eigenen Produktzyklus'. Hier will Intel das Tick-Tock-Modell quasi wiederbeleben. Tick-Tock hieß in früheren Tagen, dass auf einen Shrink in der Fertigungstechnologie im 1. Jahr (zum Beispiel 32 auf 22 nm) im 2. Jahr eine neue Architektur folgte. Diese jährliche Kadenz wurde über Jahre mehr und mehr aufgeweicht, bevor sie durch Fertigungsprobleme bei 14 nm und letztendlich bei 10 nm zu Grabe getragen wurde.

We've restored our Tick-Tock product and core cadence.

[..]

We have unquestioned performance and power performance leadership with our big cores, they will have a yearly cadence associated with it, right. And lining that up with the team so that we're delivering on products. And as you said, hey, products on set -- on 10, on 7, on 5, on 3, on 2, on 1 and blowing a sub one on a yearly beat rate.

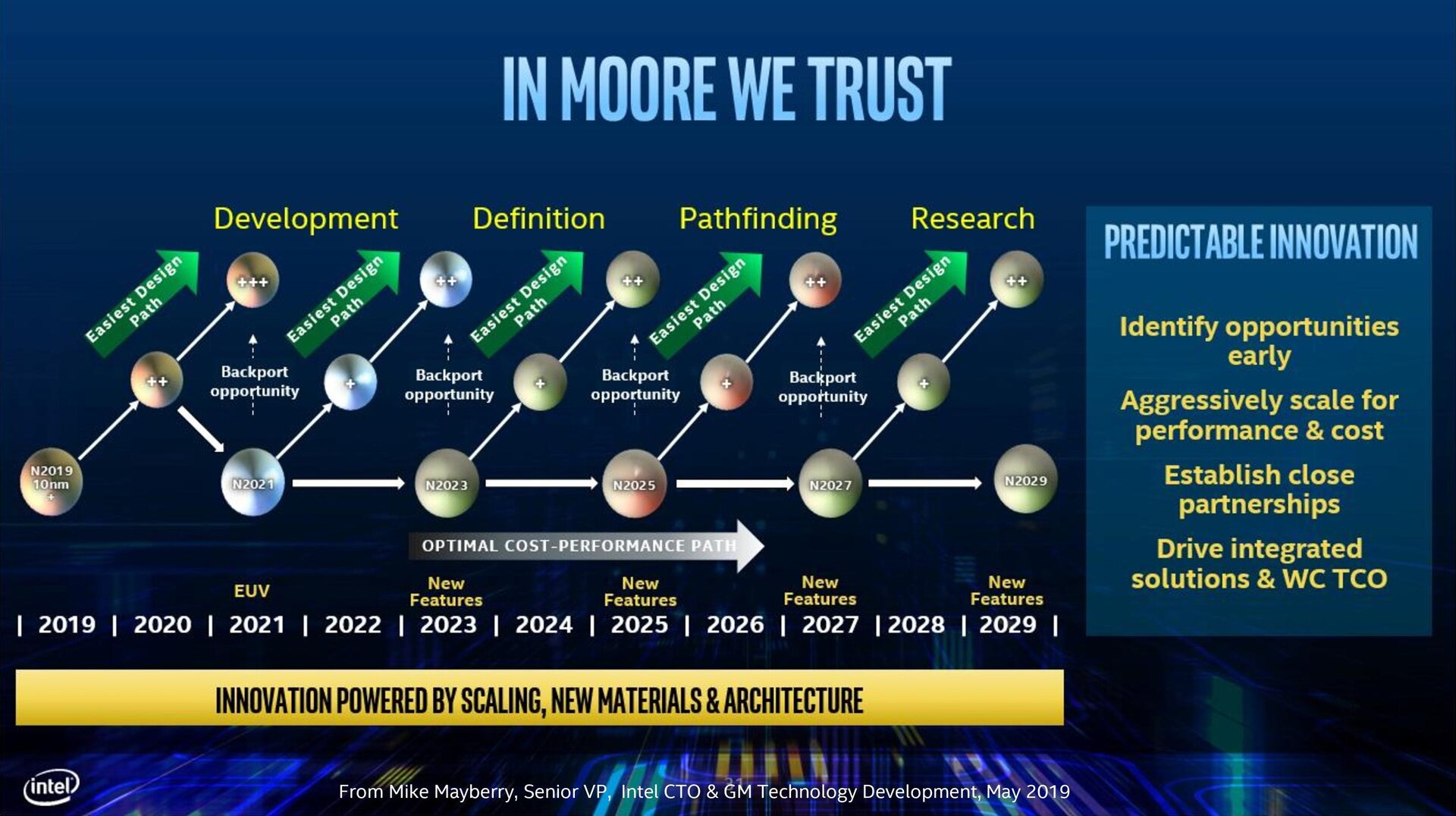

Auch wenn diese Ankündigung des ambitionierten Intel-CEOs auf den ersten Blick neu erscheinen mag, sie ist es nicht. In der Vergangenheit hatte Intel bereits wiederholt ähnliche Pläne vorgelegt, war jedoch stets am Zeitplan und der Umsetzung gescheitert. Besonders berühmt ist dabei die Roadmap aus dem Jahr 2019, die für dieses Jahr die 7-nm-EUV-Fertigung präsentierte – heute ist bekannt, dass es erst 2023 beispielsweise mit Meteor Lake soweit sein wird.

Und wenn Intel bis 2024/2025 die laut eigenen Aussagen „unbestrittene Führungsrolle“ wieder einnehmen möchte, dürfte das im Idealfall höchstens mit einer 5-nm-Fertigung passieren. Angenommen die neuen Vorhersagen stimmen, würde es die bekannte Roadmap um rund zwei Jahre nach hinten verschieben. Dass es Intel jedoch wirklich schafft, zu dem jährlichen Turnus zurückzukehren, wird der Hersteller nach vielen gerissenen Prognosen erst beweisen müssen.