Huawei und SMIC: 5-nm-Chips dank „Sechsfach-Patterning“ in Zukunft?

Huawei und seine Foundry SMIC müssen neue Wege gehen, um fortschrittliche Chips zu fertigen. Mit viel mehr Spacern geht theoretisch etwas, doch die Frage nach der technischen Umsetzung und Ausbeute steht auf einem ganz anderen Blatt. Hier haben sich andere Firmen zuvor bereits die Zähne ausgebissen.

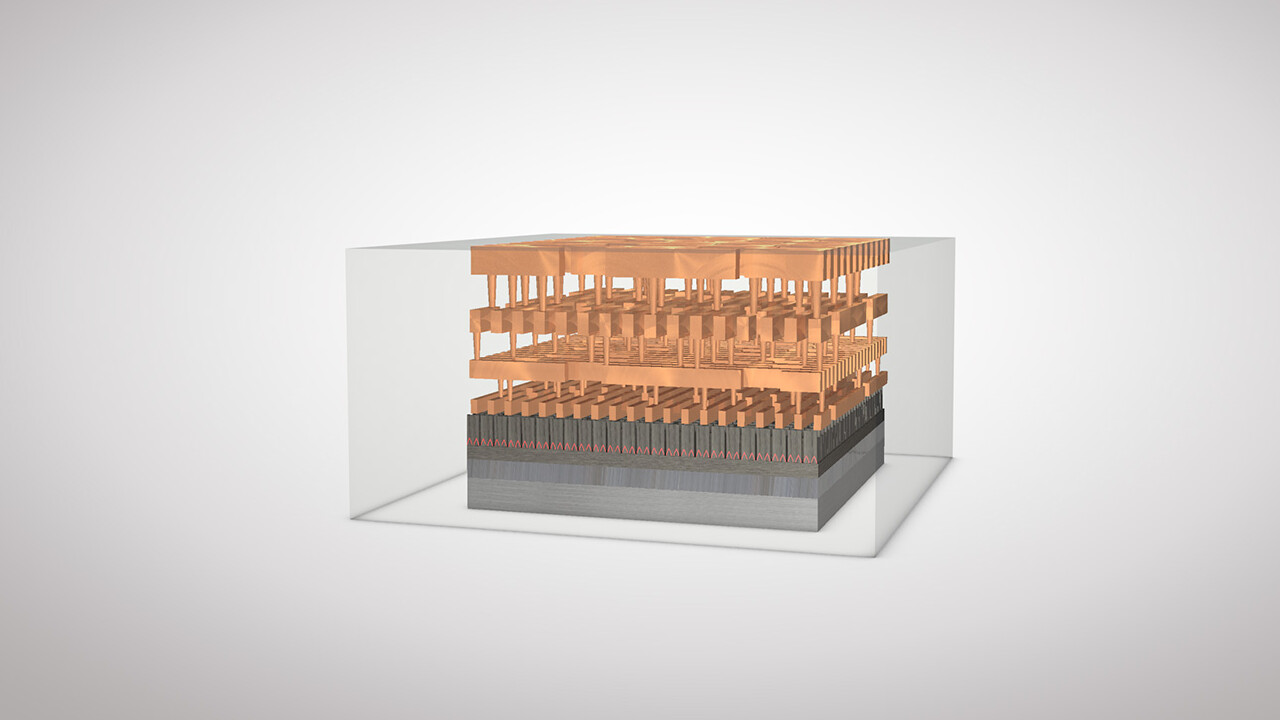

5-nm-Chips sind der nächste Traum von Huawei, der Chipsparte HiSilicon und SMIC als Fertiger. Nach dem Achtungserfolg mit dem 7-nm-Chip im letzten Jahr muss nun der nächste Fortschritt her. Doch das ist gar nicht so einfach, da die neuesten Belichtungssysteme nicht zur Verfügung stehen, mit denen TSMC, Samsung, Intel & Co ihre Chips fertigen. Die chinesischen Unternehmen wollen dennoch einen Weg finden.

Geht es auch ohne EUV oder gar High-NA-EUV?

Ein großes Problem, was Huawei und SMIC aktuell haben, ist die besagte Beschränkung auf DUV-Systeme und keinen Zugang zu fortschrittlichen Scanner mit EUV-Lithografie und in Zukunft noch besserem. Sogar die besten DUV-Systeme sind seit diesem Jahr gesperrt, man muss mit dem leben, was man hat.

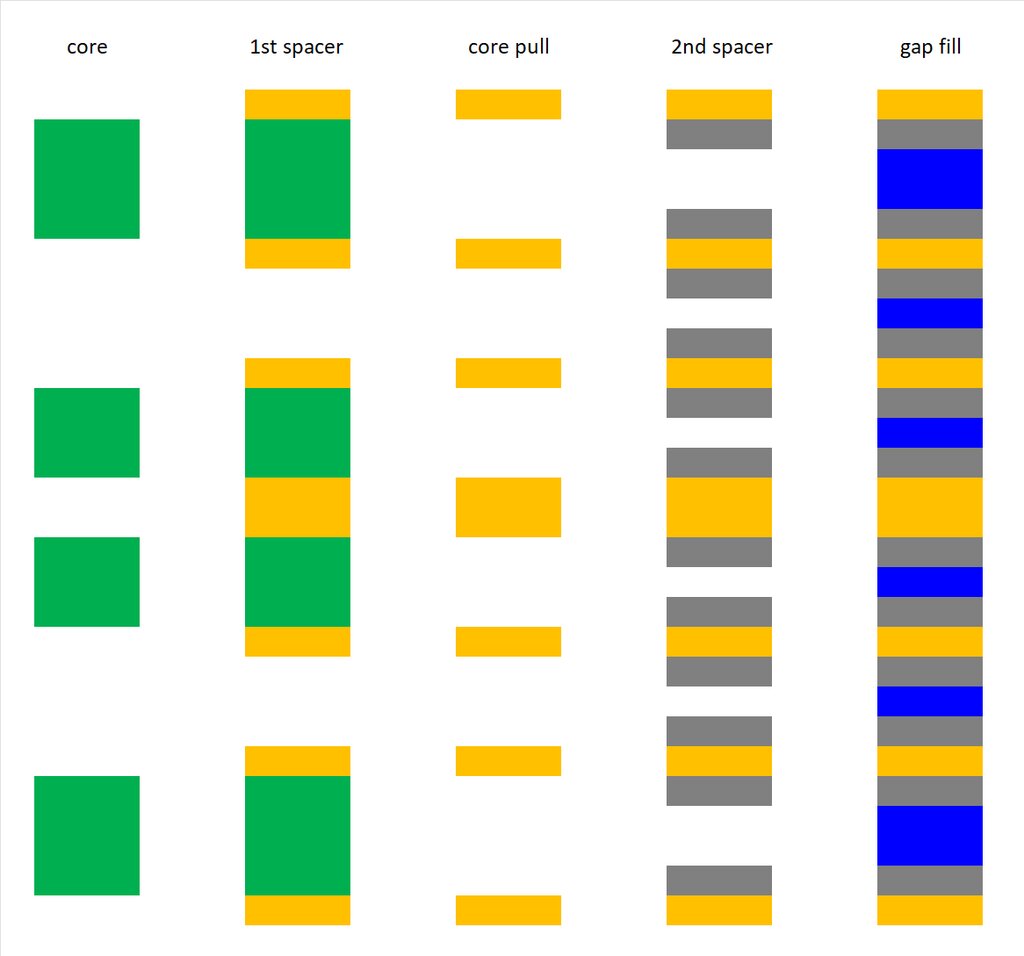

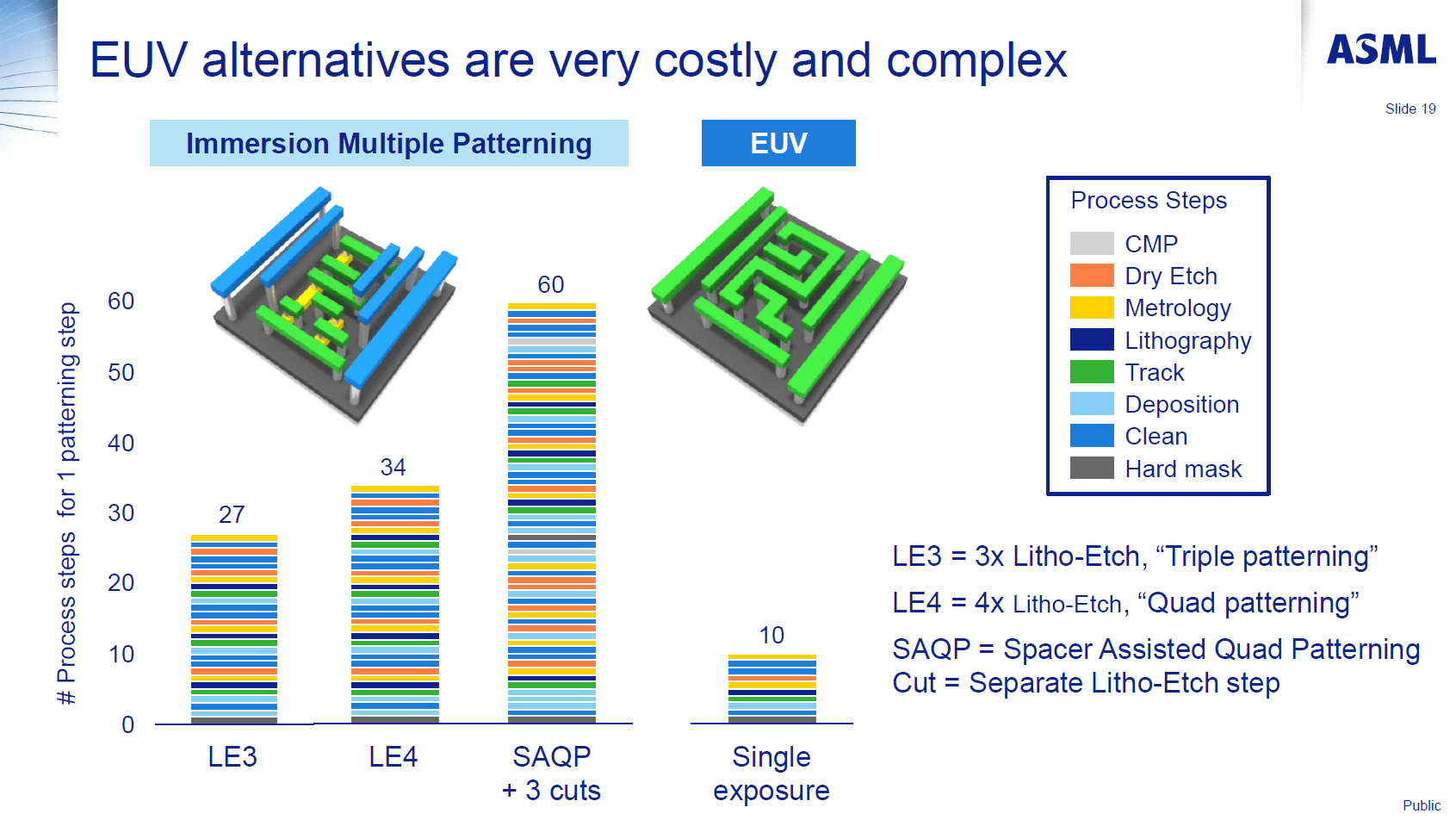

Und diese Not macht erfinderisch, zumindest reicht es bereits zu einem Patent. Darin beschreibt Huawei, wie es möglich wäre, den Pitch noch weiter zu reduzieren, ohne dabei EUV oder gar High-NA-EUV zu nutzen. Dafür wird der Einsatz von Spacern noch viel weiter ausgebaut, als er schon beim Spacer Assisted Quad-Patterning (SAQP) genutzt wird. Das Patent beschreibt so den Einsatz von bis zu fünf Spacern und macht es so in der Theorie möglich, noch kleinere Strukturen zu fertigen.

Doch was in der Theorie gut aussieht, ist in der Praxis eine ganz andere Sache. Denn die Umsetzung erfordert unzählige zusätzliche Schritte in der Fertigung, die alle wiederum einen Fehler einbauen können und so den Chip am Ende unbrauchbar machen würden. Das war bereits beim Spacer Assisted Quad-Patterning (SAQP) ein echtes Problem, weshalb EUV ja auch genau hier ins Spiel kam. Nun quasi ein „Sechsfach-Patterning“, fachlich gesprochen Spacer based self-aligned sextuple patterning (SASP), als Alternative anzubieten, dürfte wirtschaftlich betrachtet ein enormes Risiko darstellen.

Dieses und andere Patente aus den letzten Tagen werden in der Branche bereits heiß diskutiert. Denn auch dort geht man von quasi einer Lösung aus, die aktuell nahezu unmöglich in hoher Ausbeute zu fertigen ist, da es sehr viele potenzielle Fehlerquellen gibt.

[..] the problem is that it requires too many masks (7-8), and the yield may be close to 0! The critical issue is not density multiplicaion such as 2x or 4x, it is the very small cuts/blocks and vias (12-16nm) that need to be self-aligned, otherwise they will miscut/mis-connect the wrong metal lines. The real shock is HiSilicon has a 7x (SASP which can drive down metal pitch to 12nm) patent that incorporate self-aligned vias & cuts (WIPO patent application # CN2022/097621).

chenyj, SemiWiki-Foum

Für Interessierte gibt auch der deutsche Wikipedia-Artikel zum Thema Mehrfachstrukturierung (engl. Multi Patterning) einige interessante Grundlagen und Details. Dieser geht zwar nur bis zum Double-Patterning, nimmt sich aber auch des Thema Spacer und theoretischer Skalierung an und zeigen schon hier mögliche Probleme auf, die beim Ausbau aller Schritte entstehen können. Die Sorgen und Befürchtungen in den Branchenforen kommen deshalb nicht von ungefähr.